今天來講個題目,那就是收 Rs232的訊號,鮑率我們就設定 115200 ,clk速度 24MHz

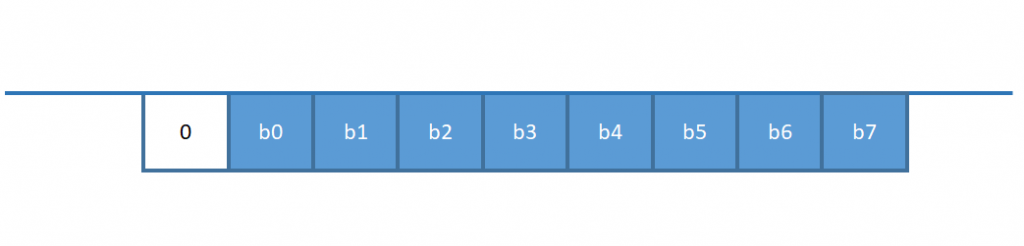

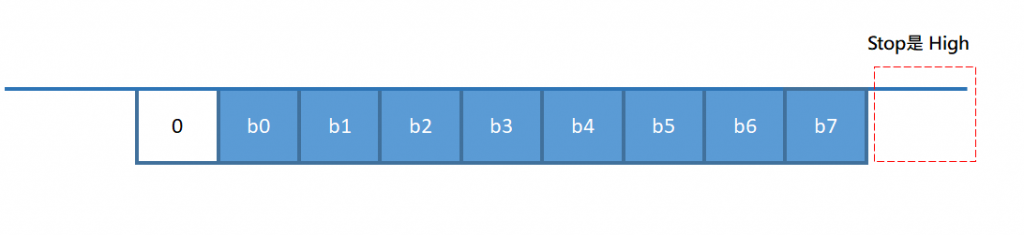

我們先來看看訊號大概長怎樣

沒訊號時

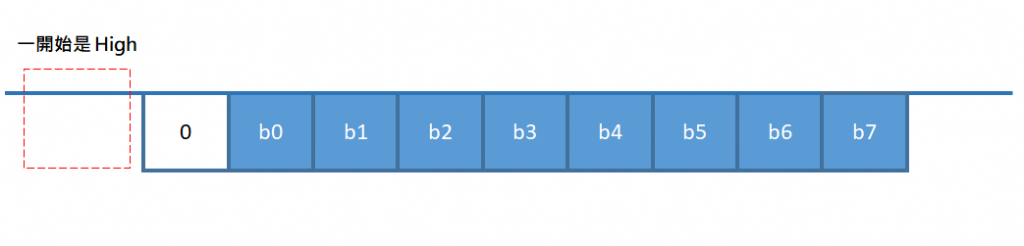

都還沒訊號時,一開始是 High

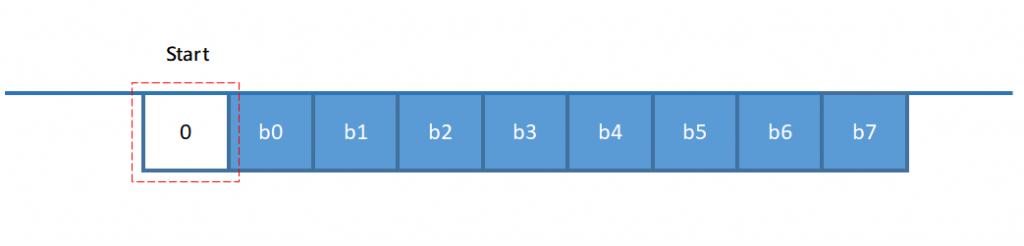

Start

拉低之後就是 Start

(PS I2C也對Start 滿重要的)

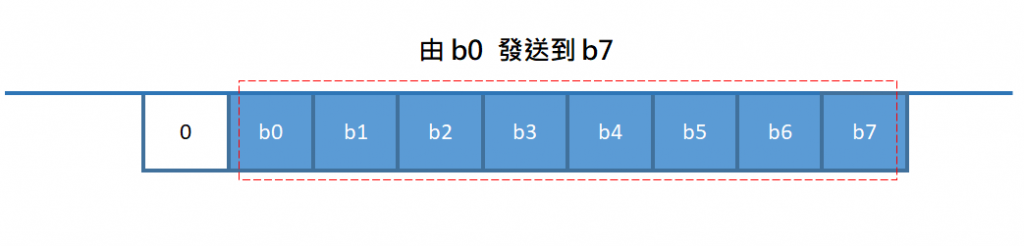

發送訊號

接下來由 b0 發送到 b7 的訊號

Stop

最後在拉高,表示 Stop

傳送的典型的鮑率

Wiki是這樣解釋的: 是指從一裝置發到另一裝置的傳符號率,即每秒鐘多少符號

典型的鮑率是300, 1200, 2400, 9600, 19200, 115200等,通常這個設定錯誤,就會收到怪怪的東西

題目分析

我們這次題目是 115200 ,clk速度 24MHz

那也就是說

clk速度 24MHz → 一個 clk是 1/24M 秒

鮑率 115200 → 一秒鐘 115200 訊號 → 一個 訊號 是 1/115200 秒

那一個訊號有幾個 Clk呢:

(訊號 是 1/115200 秒) / (一個 clk是 1/24M 秒) = 24M/115200 = 208 個 clk

最後我們看看 208 = 8b11010000 → 所以基礎訊號是 8個bit